# cronologic

Ndigo6G-12

**Product Brief**

# Introduction

The Ndigo6G-12 offers 6400Msps sample rate, 12 bits resolution and a greatly improved readout rate of 6000MB/s.

The unit is a combined ADC/TDC board for the acquisition of pulses in time of flight applications. It builds on the established Platform of the Ndigo5G-10 but takes it to the next level both in performance and flexibility.

The Ndigo6G-12 was specifically designed for time of flight applications like LIDAR or TOF mass spectrometry. Pulse arrival times can be measured with an accuracy down to 5 ps together with information on pulse shape such as area or amplitude.

Four channels with 1600 Msps at 12 Bit resolution can be acquired independently or combined to two or four channels or one channel with higher dynamic range or up to 6400 Msps.

| Technical Data                                  |                                          |

|-------------------------------------------------|------------------------------------------|

| Optimized for                                   | TOF applications                         |

| ADC channels                                    | 4                                        |

| TDC channels                                    | 4                                        |

| Gating channels                                 | 4                                        |

| Connectors                                      | 10x LEMO 00                              |

| Sample rate single channel                      | 6400 Msps                                |

| Sample rate multi channel                       | 1600 Msps                                |

| Resolution                                      | 12 bits                                  |

| Double pulse resolution                         | typically 4ns                            |

| Maximum bandwith                                | TBD                                      |

| TDC bin size                                    | 12 ps                                    |

| Multihit                                        | unlimited                                |

| Dead time between Groups                        | none                                     |

| TDC readout rate                                | 30 Mhits/s total; 11,6 Mhits/s           |

| ADC readout rate                                | approx. 6000 MByte/s                     |

| Range                                           | 106 d                                    |

| Common start/stop                               | yes / yes                                |

| Number of boards that can be event-synchronized | 8                                        |

| Readout interface                               | PCle3 x8                                 |

| Time base                                       | 50 ppb on board or external 10 MHz clock |

| On-board calibration data storage               | ✓                                        |

| Adjustable trigger windows                      | ✓                                        |

| Overlapping events possible                     | ✓                                        |

| Easy to use Windows C API                       | ✓                                        |

| In-system firmware update                       | ✓                                        |

## **Features**

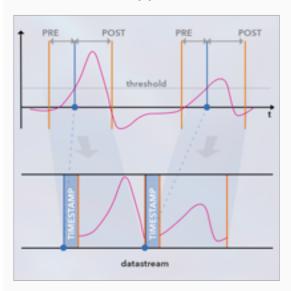

#### **Zero suppression**

Detect pulses above a certain threshold and only acquire the relevant data to massively reduce the amount of data that needs to be copied and analysed.

#### **Configurable DC Offset**

When acquiring unipolar pulses, shift the baseline to the edge of the ADC range to double your dynamic range compared with conventional ADC boards.

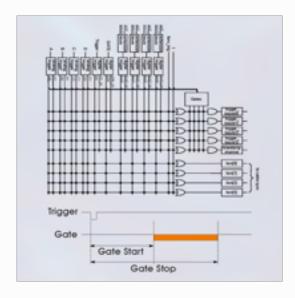

#### **Flexible Utility Functions**

A multitude of useful details help you to create a highly integrated setup with a minimum of external components. Using the integrated TiGer timing pattern generator can provide digital pulse patterns to control your experiment or internal triggers. Use gate and veto functions with our gating logic. This also works across channels or from the additional digital input with a flexible trigger matrix.

### **Streaming Architecture**

Don't pay for expensive memory upgrades! The buffers of the Ndigo6G-12 are only limited by the size of your main memory.

Data is streamed at a rate of 6000MByte/s concurrently to data acquisition. There is no dead time and latency is minimized.