为了形成范德华异质结构(vdWHs),垂直集成了二维层状材料,在这篇文章中通过低真空光电流测试技术研究垂直场效应晶体管

(VFET)的范德华异质结在不同漏极偏压,栅极偏压和金属功函数下的迁移率,WSe2中的陷阱是主要散射来源,它影响了垂直迁移

率和三种不同的传输机制:欧姆传输、陷阱受限传输和空间电荷受限传输。

展示全部

为了形成范德华异质结构(vdWHs),垂直集成了二维层状材料,在这篇文章中首先研究和设计了垂直场效应晶体管(VFET)的范德

华异质结在不同漏极偏压,栅极偏压和金属功函数下的迁移率,WSe2中的陷阱是主要散射来源,它影响了垂直迁移率和三种不同的传

输机制:欧姆传输、陷阱受限传输和空间电荷受限传输。

通过提高WSe2的费米能级来抑制陷阱态,可以提高VFET的垂直迁移率,这可以通过施加高的漏极电压来增加注入的载流子密度,或

者可以通过分别施加栅极电压和降低金属功函数来减小石墨烯/WSe2、金属/WSe2异质结的肖特基势垒来实现。

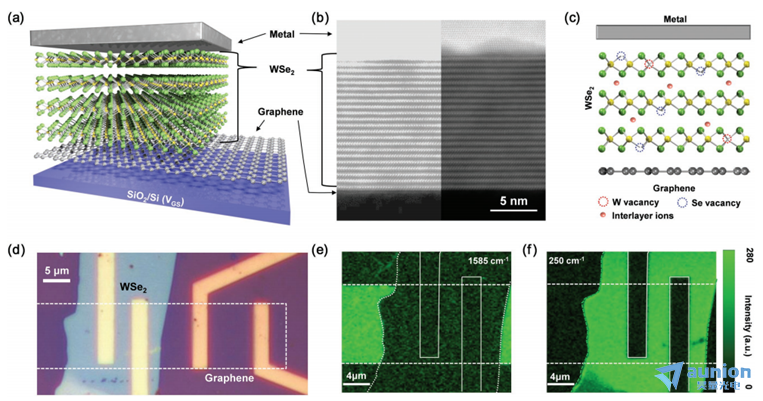

图1

图1 石墨烯/WSe2/金属垂直场效应晶体管VFET结构 a)VFET源极、沟道、漏极示意图b) 具有明亮对比度(右面)和黑暗对比度(左

面)的截面明场STEM图像 c) 石墨烯/ WSe2 /金属VFET中的陷阱源示意图 d) 器件的光学图像,显示底部石墨烯层(虚线),顶部金

属电极(虚线)以及中间WSe2层 e)石墨烯拉曼成像(1585cm-1)f)WSe2拉曼成像(250cm-1)。

电荷载流子的迁移率是由WSe2中陷阱的散射决定的,这是由层间间隙中的Se和W空位或离子化杂质引起的(图1c)。

图1d显示了一个典型的石墨烯/ WSe2 /金属异质结构器件的光学图像,该器件具有位于WSe2薄片下方的12 µm宽的石墨烯(虚线)。

图1e,f显示了石墨烯的G峰强度(图1e中为1585 cm-1)和WSe2的E12g + A1g峰(图1f中为250 cm-1)的拉曼成像图,这清楚地辨别

了石墨烯、WSe2和金属电极的堆叠区域。石墨烯和WSe2的拉曼峰都出现在重叠区域(图S3,支持信息)。

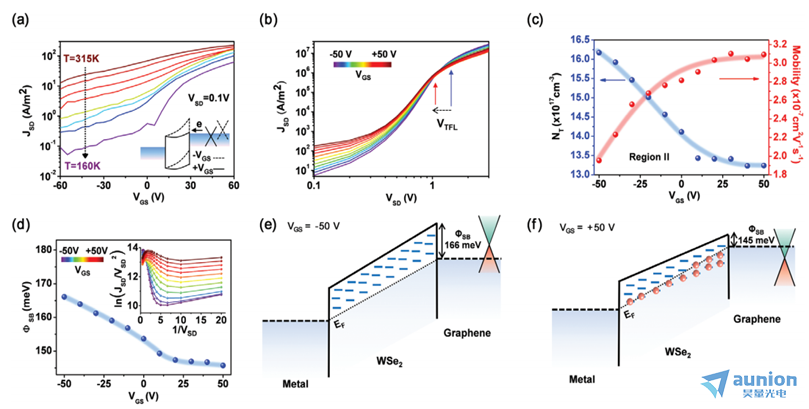

图2

图2 栅极偏压下石墨烯/WSe2/金属VFET中的陷阱填充限制载流子传导和迁移率工程a)石墨烯/WSe2/金属VFET随着温度变化的转移曲

线。插图为正栅极偏压(实线)和负栅极偏压(虚线)下石墨烯/WSe2/金属VFET的能带示意图。b)各种栅极电压下JSD-VSD的特性

曲线。c)Ⅱ区栅极电压下石墨烯/WSe2/金属VFET中的陷阱密度和迁移率。d)从ln(J(V)/V2)-1/V曲线中计算的栅极电压下的肖特基势

垒。e,f)在VGS=-50V和50V时石墨烯/WSe2/金属VFET的能带示意图。

石墨烯/WSe2界面处的肖特基势垒可以调制电流(图3a的插图)。

正的栅极电压可有效降低石墨烯/WSe2肖特基势垒高度,从而促进电子的欧姆传输。相反,负栅极电压增加了肖特基势垒的高度,从

而通过热电子发射抑制了肖特基势垒上的电子传输。

开关比随着温度的降低从315K的10增加到160K的103(图3a),这归因于在off状态下肖特基势垒上热电子发射的减少。

图3

图3 不同金属功函数的石墨烯/WSe2/金属VFET的陷阱填充限制载流子传导和迁移率工程a)Au,Al,Mn金属电极的石墨烯/WSe2/金属

VFET的JSD-VSD特性曲线。插图展示了在单层WSe2薄片上的三种不同金属电极的VFET。b)Au,Al,Mn金属电极的VFET的ln(J(V)/V2)

曲线和计算的肖特基势垒。c)Au,Al,Mn金属电极的VFET的能带示意图和陷阱态。d-f) 对于Au(d),Al(e)和Mn(f)金属电极,使

用VSD和VGS以J=Vm中的指数m的曲线。g,h)Au,Al,Mn金属电极的VFET中的(g)陷阱密度(h)迁移率通过在单个WSe2薄片(图4a

的插图)上演示三种不同的金属电极(Au,Al和Mn)来控制金属/ WSe2界面处的肖特基势垒高度。

在J-V特性曲线中(图4a),Mn电极显示整个VSD的电流最高,而Au电极中的电流最低,这归因于不同功函数金属与WSe2之间的肖

特基势垒的高度不同。

通过施加栅极电压可以进一步提高迁移率,如图3所示。Mn,Al和Au构成的异质结 随不同栅压(图S9,支撑文献)的J-Vm曲线的指数

m 分别被画在图4d-f。在所有器件中,VGS的增加,使VTFL移至更低的VSD,从而导致无陷阱SCLC区域的扩大和陷阱填充受限区域

的变窄。在较低的肖特基势垒器件中,VTFL更低,这归因于较低的陷阱密度。 图4g,h显示了在各种栅极电压下,Mn / WSe2 /石墨

烯,Al / WSe2 /石墨烯和Au / WSe2 /石墨烯器件的陷阱密度和迁移率。总体而言,Mn vdWH的陷阱密度大约是Au vdWH的四倍,在

VGS = 50 V时最小陷阱密度为5×1017cm-3。Mn vdWH中的低陷阱密度将迁移率提高到5.4× 10-5 cm2V-1 s-1,约为Au vdWH初始迁

移率的76倍。

实验部分

表征:石墨烯/WSe2/金属VFET的电学特性是在低真空条件下使用探针台通过源表(Keithley 4200)测量的, 使用Nanobase

XperRam 200拉曼成像系统测量拉曼光谱。

注:本文章翻译自:Mobility Engineering in Vertical Field Effect Transistors Based on Van der WaalsHeterostructures

期刊:Advanced Materials

作者:Shin, Yong Seon;Lee, Kiyoung;Kim, Young Rae;Lee, Hyangsook;Lee, I. Min;Kang, Won Tae;Lee, Boo Heung;Kim, Kunnyun;Heo, Jinseong;Park, Seongjun;Lee, Young Hee;Yu, Woo Jong

您可以通过我们的官方网站了解更多的产品信息,或直接来电咨询4006-888-532。